JavaScript is disabled for your browser. Some features of this site may not work without it.

Buscar en RiuNet

Listar

Mi cuenta

Estadísticas

Ayuda RiuNet

Admin. UPV

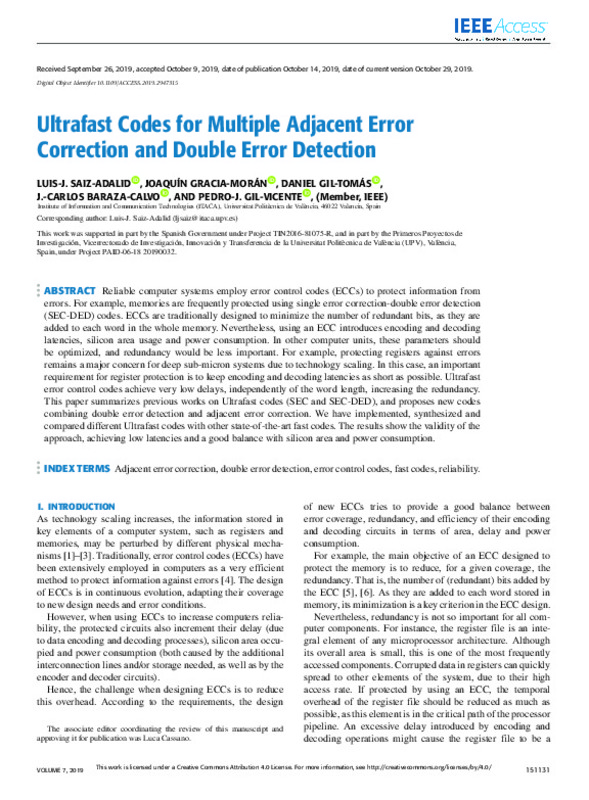

Ultrafast Codes for Multiple Adjacent Error Correction and Double Error Detection

Mostrar el registro sencillo del ítem

Ficheros en el ítem

| dc.contributor.author | Saiz-Adalid, Luis-J.

|

es_ES |

| dc.contributor.author | Gracia-Morán, Joaquín

|

es_ES |

| dc.contributor.author | Gil Tomás, Daniel Antonio

|

es_ES |

| dc.contributor.author | Baraza Calvo, Juan Carlos

|

es_ES |

| dc.contributor.author | Gil, Pedro

|

es_ES |

| dc.date.accessioned | 2020-05-23T03:00:39Z | |

| dc.date.available | 2020-05-23T03:00:39Z | |

| dc.date.issued | 2019-10-14 | es_ES |

| dc.identifier.uri | http://hdl.handle.net/10251/144214 | |

| dc.description | (c) 2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works. | es_ES |

| dc.description.abstract | [EN] Reliable computer systems employ error control codes (ECCs) to protect information from errors. For example, memories are frequently protected using single error correction-double error detection (SEC-DED) codes. ECCs are traditionally designed to minimize the number of redundant bits, as they are added to each word in the whole memory. Nevertheless, using an ECC introduces encoding and decoding latencies, silicon area usage and power consumption. In other computer units, these parameters should be optimized, and redundancy would be less important. For example, protecting registers against errors remains a major concern for deep sub-micron systems due to technology scaling. In this case, an important requirement for register protection is to keep encoding and decoding latencies as short as possible. Ultrafast error control codes achieve very low delays, independently of the word length, increasing the redundancy. This paper summarizes previous works on Ultrafast codes (SEC and SEC-DED), and proposes new codes combining double error detection and adjacent error correction. We have implemented, synthesized and compared different Ultrafast codes with other state-of-the-art fast codes. The results show the validity of the approach, achieving low latencies and a good balance with silicon area and power consumption. | es_ES |

| dc.description.sponsorship | This work was supported in part by the Spanish Government under Project TIN2016-81075-R, and in part by the Primeros Proyectos de Investigacion, Vicerrectorado de Investigacion, Innovacion y Transferencia de la Universitat Politecnica de Valencia (UPV), Valencia, Spain, under Project PAID-06-18 20190032. | es_ES |

| dc.language | Inglés | es_ES |

| dc.publisher | Institute of Electrical and Electronics Engineers | es_ES |

| dc.relation.ispartof | IEEE Access | es_ES |

| dc.rights | Reconocimiento (by) | es_ES |

| dc.subject | Adjacent error correction | es_ES |

| dc.subject | Double error detection | es_ES |

| dc.subject | Error control codes | es_ES |

| dc.subject | Fast codes | es_ES |

| dc.subject | Reliability | es_ES |

| dc.subject.classification | ARQUITECTURA Y TECNOLOGIA DE COMPUTADORES | es_ES |

| dc.title | Ultrafast Codes for Multiple Adjacent Error Correction and Double Error Detection | es_ES |

| dc.type | Artículo | es_ES |

| dc.identifier.doi | 10.1109/ACCESS.2019.2947315 | es_ES |

| dc.relation.projectID | info:eu-repo/grantAgreement/UPV//PAID-06-18/ | es_ES |

| dc.relation.projectID | info:eu-repo/grantAgreement/MINECO//TIN2016-81075-R/ES/MECANISMOS DE ADAPTACION CONFIABLE PARA VEHICULOS AUTONOMOS Y CONECTADOS/ | es_ES |

| dc.relation.projectID | info:eu-repo/grantAgreement/UPV//SP20180334/ | es_ES |

| dc.rights.accessRights | Abierto | es_ES |

| dc.contributor.affiliation | Universitat Politècnica de València. Departamento de Informática de Sistemas y Computadores - Departament d'Informàtica de Sistemes i Computadors | es_ES |

| dc.description.bibliographicCitation | Saiz-Adalid, L.; Gracia-Morán, J.; Gil Tomás, DA.; Baraza Calvo, JC.; Gil, P. (2019). Ultrafast Codes for Multiple Adjacent Error Correction and Double Error Detection. IEEE Access. 7:151131-151143. https://doi.org/10.1109/ACCESS.2019.2947315 | es_ES |

| dc.description.accrualMethod | S | es_ES |

| dc.relation.publisherversion | https://doi.org/10.1109/ACCESS.2019.2947315 | es_ES |

| dc.description.upvformatpinicio | 151131 | es_ES |

| dc.description.upvformatpfin | 151143 | es_ES |

| dc.type.version | info:eu-repo/semantics/publishedVersion | es_ES |

| dc.description.volume | 7 | es_ES |

| dc.identifier.eissn | 2169-3536 | es_ES |

| dc.relation.pasarela | S\398481 | es_ES |

| dc.contributor.funder | Universitat Politècnica de València | es_ES |

| dc.contributor.funder | Ministerio de Economía y Competitividad | es_ES |