Listar por autor "Saiz Adalid, Luis José"

RiuNet: Repositorio Institucional de la Universidad Politécnica de Valencia

- RiuNet repositorio UPV

- :

- Listar por autor

JavaScript is disabled for your browser. Some features of this site may not work without it.

Buscar en RiuNet

Listar

Mi cuenta

Ayuda RiuNet

Admin. UPV

Listar por autor "Saiz Adalid, Luis José"

Mostrando ítems 1-20 de 33

-

Gil Tomás, Daniel Antonio; Gracia-Morán, Joaquín; Baraza Calvo, Juan Carlos; Saiz-Adalid, Luis-J.; Gil, Pedro (Institute of Electrical and Electronics Engineers (IEEE), 2012-12)Intermittent faults, being serious concerns for deep-submicron integrated circuits, are not well studied in the literature. This paper performs fault injection simulation to analyze the impact of intermittent faults, which ...

-

Polo Esteve, Jaime Manuel (Universitat Politècnica de València, 2015-10-14)[ES] Los controladores MIDI permiten la gestión hardware del software musical. Como un teclado MIDI permite la entrada de notas a un secuenciador MIDI, cuando se carga un proyecto en el secuenciador o cuando se ...

-

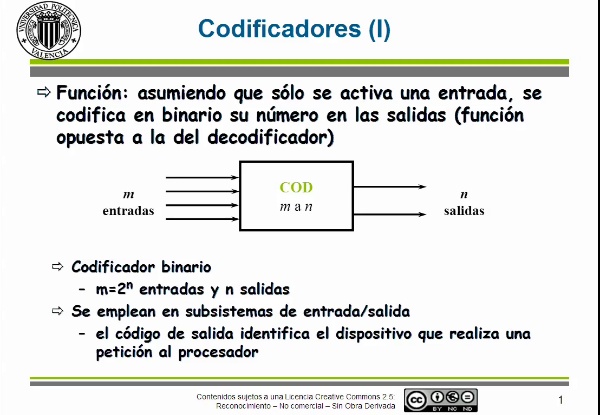

Saiz Adalid, Luis José (Universitat Politècnica de València, 2009-06-09)El vídeo presenta los conceptos necesarios para comprender el funcionamiento y ser capaz de diseñar los circuitos combinacionales denominados codificadores.

-

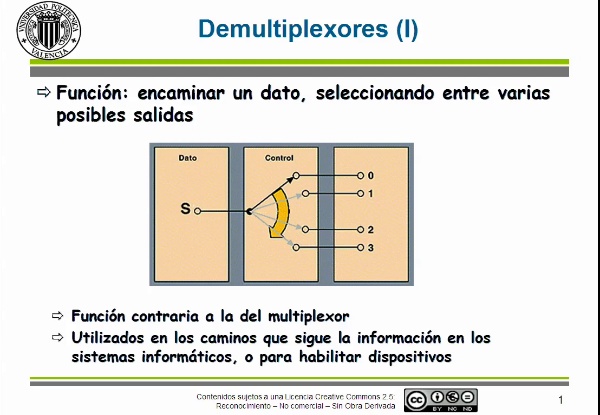

Saiz Adalid, Luis José (Universitat Politècnica de València, 2009-06-09)Este vídeo presenta los circuitos combinacionales denominados demultiplexores. Explica su diseño y funcionamiento.

-

Vicente García, Adrián (Universitat Politècnica de València, 2023-07-26)[ES] Este trabajo consiste en la utilización de dos prototipos de vehículos autónomos no tripulados, ambos con un sistema de conducción basado en Arduino y equipados con distintos sensores, que serán capaces de comunicarse ...

-

Juárez Pérez, Arantxa (Universitat Politècnica de València, 2021-02-11)[ES] Desarrollo de un sistema (metodología y software) para el diseño digital de brazos protésicos a partir de un modelo base. El modelo se adecuará a las necesidades de cada individuo. La idea es desarrollar un sistema ...

-

Sebastián Rebollar, Francisco (Universitat Politècnica de València, 2016-09-14)[ES] El presente documento incluye una extensa explicación del proceso proyectual llevado a cabo al realizar una aplicación de gestión de proyectos para una empresa internacional del sector del automóvil. A lo largo de ...

-

Martínez Ruiz, Carmelo (Universitat Politècnica de València, 2021-02-01)[ES] En este trabajo se realiza un estudio sobre los sistemas empotrados con propiedades de tolerancia a fallos mediante la protección del sistema por Códigos de Corrección de Errores (ECC). En concreto, se pretende proteger ...

-

Martín Tabares, Pablo (Universitat Politècnica de València, 2021-04-19)[ES] Durante estos últimos años, el desarrollo tecnológico ha propiciado un aumento en las prestaciones de los sistemas digitales, pero a costa de reducir su confiabilidad. Por ejemplo, y gracias a la continua reducción ...

-

Gracia-Morán, Joaquín; Saiz-Adalid, Luis-J.; Baraza-Calvo, Juan-Carlos; Gil Tomás, Daniel Antonio; Gil, Pedro (Institute of Electrical and Electronics Engineers, 2021-11)[EN] The continuous raise in the integration scale of CMOS technology has provoked an augment in the fault rate. Particularly, computer memory is affected by Single Cell Upsets (SCU) and Multiple Cell Upsets (MCU). A common ...

-

Diago Gallardo, Daniel (Universitat Politècnica de València, 2012-09-27)Con el siguiente proyecto se propone un nuevo diseño de chasis para PC, en este caso se va a centrar en mejorar su eficiencia tanto calorífica como sonora, intentando conseguir un diseño nuevo de componente hardware altamente ...

-

Garrigues Carbó, Pau (Universitat Politècnica de València, 2019-06-10)[ES] En este proyecto se realiza el diseño e implementación de un clasi cador basado en redes neuronales convolucionales con el objetivo de realizar el etiquetado de objetos 3D con el objetivo de alimentar un sistema de ...

-

Quiles Alemañ, José (Universitat Politècnica de València, 2020-04-08)[ES] El presente Trabajo Fin de Máster se encuentra directamente alineado con el proyecto bIoTope, financiado por la Unión Europea, que pretende construir un ecosistema abierto y de innovación donde las empresas puedan ...

-

Amador Labrador, Pablo (Universitat Politècnica de València, 2019-09-24)[ES] El presente trabajo tiene como objetivo el diseño del sistema de seguimiento de un robot móvil que servirá como plataforma de pruebas simplificada para vehículos autónomos. Para ello se utilizarán dos robots, los ...

-

Rubio Cuenca, Ángeles (Universitat Politècnica de València, 2021-03-24)[ES] En este proyecto se realizará el diseño y desarrollo de un sistema capaz de medir la temperatura y humedad de una sala. Para ello se diseñará la electrónica necesaria basada en una placa base con microcontrolador ...

-

Gracia-Morán, Joaquín; Baraza Calvo, Juan Carlos; Gil Tomás, Daniel Antonio; Saiz-Adalid, Luis-J.; Gil, Pedro (Institute of Electrical and Electronics Engineers (IEEE), 2014-01-24)With the scaling of complementary metal-oxide-semiconductor (CMOS) technology to the submicron range, designers have to deal with a growing number and variety of fault types. In this way, intermittent faults are gaining ...

-

Saiz Adalid, Luis José (Universitat Politècnica de València, 2016-01-07)[EN] From the first integrated circuit was developed to very large scale integration (VLSI) technology, the hardware of computer systems has had an immense evolution. Moore's Law, which predicts that the number of transistors ...

-

Gil Tomás, Daniel Antonio; Gracia-Morán, Joaquín; Saiz-Adalid, Luis-J.; Gil, Pedro (MDPI AG, 2019-07-31)[EN] Due to the increasing defect rates in highly scaled complementary metal-oxide-semiconductor (CMOS) devices, and the emergence of alternative nanotechnology devices, reliability challenges are of growing importance. ...

-

Bazán Andría, Julián (Universitat Politècnica de València, 2022-10-13)[ES] La modificación de los pesos de una red neuronal en plena ejecución de un proceso industrial puede llevar a resultados inesperados; probablemente no alineados con el objetivo de la cadena productiva, que pueden ...

-

Gracia-Morán, Joaquín; Saiz-Adalid, Luis-J.; Gil Tomás, Daniel Antonio; Gil, Pedro (Institute of Electrical and Electronics Engineers, 2018)[EN] Currently, faults suffered by SRAM memory systems have increased due to the aggressive CMOS integration density. Thus, the probability of occurrence of single-cell upsets (SCUs) or multiple-cell upsets (MCUs) ...

Mostrando ítems 1-20 de 33

Universitat Politècnica de València. Unidad de Documentación Científica de la Biblioteca (+34) 96 387 70 85 · RiuNet@bib.upv.es