Listar por palabra clave "Verilog"

RiuNet: Repositorio Institucional de la Universidad Politécnica de Valencia

- RiuNet repositorio UPV

- :

- Listar por palabra clave

JavaScript is disabled for your browser. Some features of this site may not work without it.

Buscar en RiuNet

Listar

Mi cuenta

Ayuda RiuNet

Admin. UPV

Listar por palabra clave "Verilog"

Mostrando ítems 1-20 de 33

-

Martínez Sánchez, Pablo (Universitat Politècnica de València, 2021-10-11)[ES] El objetivo del presente trabajo es adaptar un core IP de un microprocesador RISC-V segmentado para que pueda ser usado en sistemas SOC basados en buses Avalon. El core IP adaptado implementa una arquitectura ...

-

Gadea Gironés, Rafael (2024-06-13)Paso de ASM de tipo Mealy a una descripción Verilog fundamentalmente constituida por un proceso always que describe conjuntamente Control-Path y acciones del Data-path

-

Gadea Gironés, Rafael (2024-06-20)Paso de un ASM Moore a código Verilog, eludiendo poner jerarquía pero separando claramente los elementos de data-path y control-path

-

Lozano Torres, Raúl (Universitat Politècnica de València, 2021-12-14)[ES] High Level Synthesis (HLS) aparece como un nuevo paradigma para el diseño de sistemas digitales, en el que la funcionalidad del circuito se describe utilizando lenguajes de alto nivel como C o C++, y las herramientas ...

-

Antequera Cañadas, Pedro (Universitat Politècnica de València, 2019-10-09)[ES] El TFG consiste en proponer un diseño para un bloque compresor de imágenes basado un esquema de Transformada Wavelet + Cuantificador. El objetivo se centra en intentar conseguir ratios de compresión inferiores o ...

-

Andreu Cerezo, Pablo (Universitat Politècnica de València, 2020-07-30)[EN] Artificial intelligence aims to solve much of the problems of the contemporary society that we live in. But, in order for it to be ever so prevalent, the development of efficient inference-specific chips is needed, ...

-

Seguí Pérez, Mireia (Universitat Politècnica de València, 2023-10-05)[ES] El presente trabajo de fin de grado ha sido desarrollado en la empresa Maxlinear. El objetivo de este es desarrollar el diseño de una Verificacion IP (VIP) para comprobar el funcionamiento de interfaces que utilicen ...

-

Cuevas López, Aarón (Universitat Politècnica de València, 2022-01-17)[ES] La electrofisiología extracelular es una técnica ampliamente usada en investigación neurocientífica, la cual estudia el funcionamiento del cerebro mediante la medición de campos eléctricos generados por la actividad ...

-

Gadea Gironés, Rafael (2023-06-06)Realización mediante de funciones en VHDL mediante tablas

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2023-06-06)Diseño de funciones con HDL: Tratamiento de punto flotante

-

Talens Felis, Juan Bautista (Universitat Politècnica de València, 2020-02-11)[ES] El trabajo final de máster consiste en la captura de señales analógicas mediante la tarjeta de adquisición DE1-SoC para su uso en narices electrónicas. Se trata de la implementación hardware de un sistema completo de ...

-

Giménez Aparisi, Guillem (Universitat Politècnica de València, 2021-02-18)[ES] El proyecto consiste en el desarrollo de un circuito digital para la obtención en tiempo real del árbol de códigos Huffman para la compresión de datos del plano de energía del experimento NEXT. El objetivo es la ...

-

Barreras Almarcha, Héctor (Universitat Politècnica de València, 2021-10-11)[ES] Proponemos una solución de librerías software para habilitar el análisis, modificación y virtualización programáticos de lenguajes de descripción hardware con el principal objetivo de aumentar la productividad de los ...

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2015-03-09)En este objeto puede verse la estructura de un célula lógica de un dispositivo programable, así como dicha célula es configurada a partir de un código Verilog sencillo de un generador de paridad. Este objeto también demuestra ...

-

Gadea Gironés, Rafael (2021-06-07)Descripción de FSM en Verilog mediante un solo proceso

-

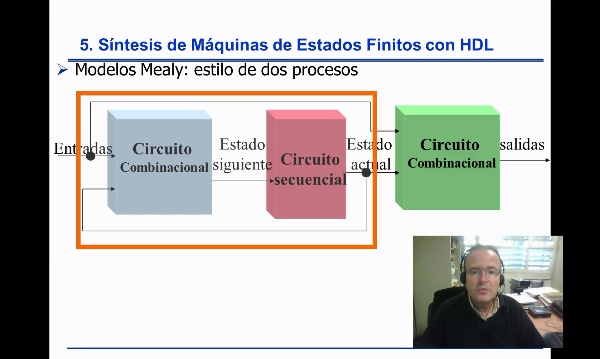

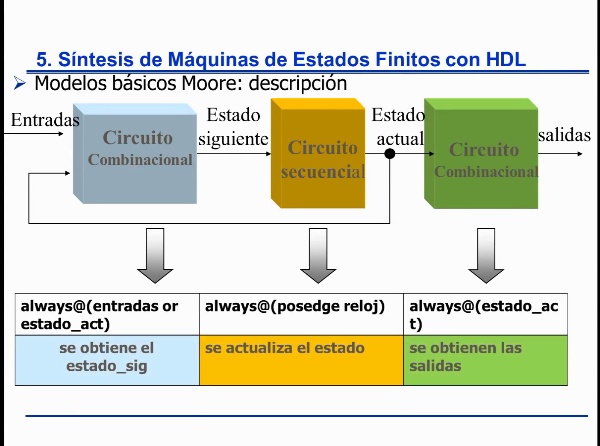

Gadea Gironés, Rafael (Universitat Politècnica de València, 2015-06-03)En este objeto se describe el método de descripción de las Máquinas de Estados Finitos con Verilog. El modelo de máquina es Mealy. El estilo utilizado es un estilo de dos procesos

-

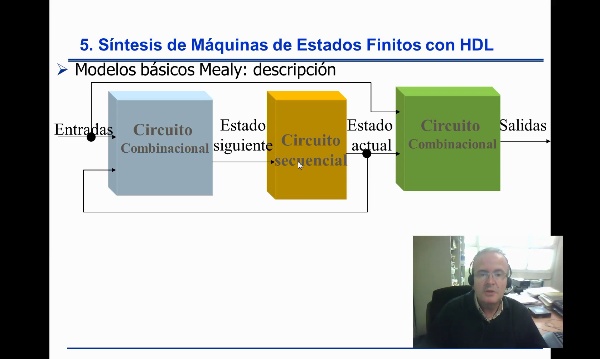

Gadea Gironés, Rafael (Universitat Politècnica de València, 2015-06-03)En este video se modliza una FSM Mealy mediante Verilog, aplicando el estilo de tres procesos (always), dos de los cuales son de tipo combinacional y un tercero de tipo secuencial

-

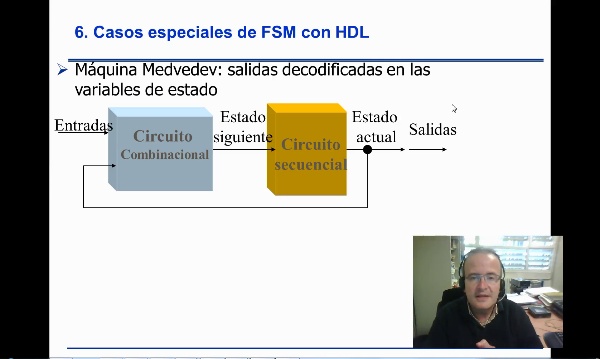

Gadea Gironés, Rafael (Universitat Politècnica de València, 2015-06-03)En este video se modliza una FSM Medvedev mediante Verilog, aplicando diferentes estilos; pero consiguiendo en todos ellos evitar la realización del circuito combinacional de salida

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2015-06-03)En este video se modliza una FSM Moore mediante Verilog, aplicando el estilo de dos procesos (always), uno de los cuales es de tipo combinacional y un segundo de tipo secuencial

-

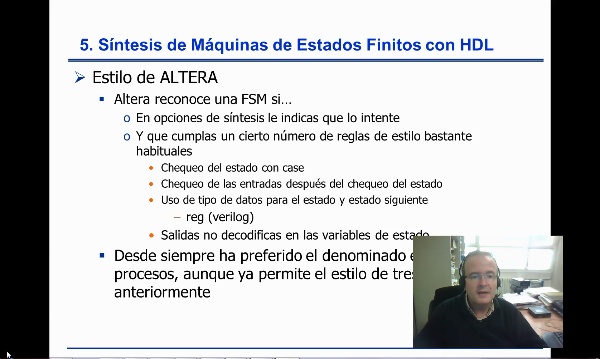

Gadea Gironés, Rafael (Universitat Politècnica de València, 2015-03-09)En este vídeo se describe el estilo de implementación en Verilog de una máquina de estados (FSM) mediante el llamado estilo de tres procesos. También se hace una breve mención de la utilidad del "pragma full_case"

Mostrando ítems 1-20 de 33

Universitat Politècnica de València. Unidad de Documentación Científica de la Biblioteca (+34) 96 387 70 85 · RiuNet@bib.upv.es